# 80186/80188 HIGH-INTEGRATION 16-BIT MICROPROCESSORS

- Integrated Feature Set

- Enhanced 8086-2 CPU

- Clock Generator

- 2 Independent DMA Channels

- Programmable Interrupt Controller

- 3 Programmable 16-bit Timers

- Programmable Memory and Peripheral Chip-Select Logic

- Programmable Wait State Generator

- Local Bus Controller

- Available in 10 MHz and 8 MHz Versions

- High-Performance Processor

- 4 Mbyte/Sec Bus Bandwidth Interface @ 8 MHz (80186)

- 5 Mbyte/Sec Bus Bandwidth Interface @ 10 MHz (80186)

- Direct Addressing Capability to 1 Mbyte of Memory and 64 Kbyte I/O

- Completely Object Code Compatible with All Existing 8086, 8088 Software

— 10 New Instruction Types

- Numerics Coprocessing Capability Through 8087 Interface

- Available in 68 Pin:

- Plastic Leaded Chip Carrier (PLCC)

- Ceramic Pin Grid Array (PGA)

- Ceramic Leadless Chip Carrier (LCC)

- Available in EXPRESS

- Standard Temperature with Burn-In

- Extended Temperature Range (-40°C to +85°C)

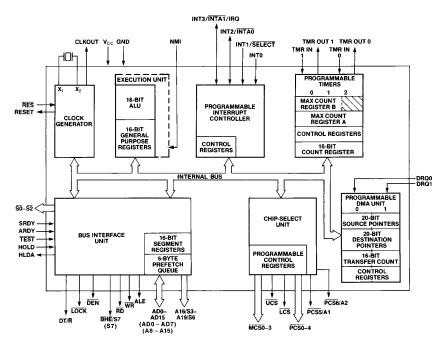

Figure 1. Block Diagram

272430-1

\*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

# 80186/80188 High-Integration 16-Bit Microprocessors

| CONTENTS                                                | PAGE   | CONTENTS                      | PAGE |

|---------------------------------------------------------|--------|-------------------------------|------|

| FUNCTIONAL DESCRIPTION                                  | 9      | ABSOLUTE MAXIMUM RATINGS      | 15   |

| Introduction                                            | 9      | D.C. CHARACTERISTICS          | 15   |

| CLOCK GENERATOR                                         |        | A.C. CHARACTERISTICS          | 16   |

| Clock Generator                                         | 9      | EXPLANATION OF THE AC SYMBOLS | 18   |

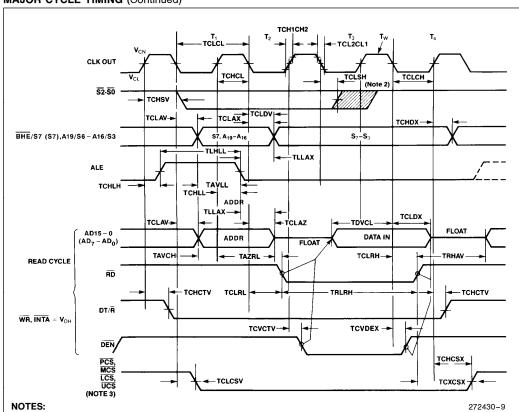

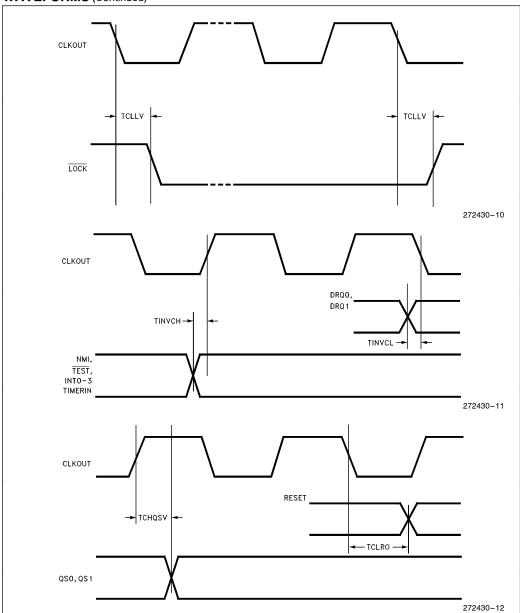

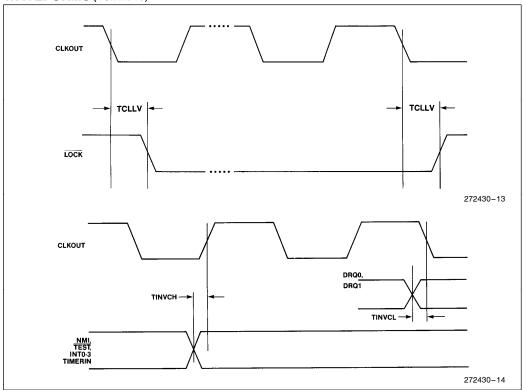

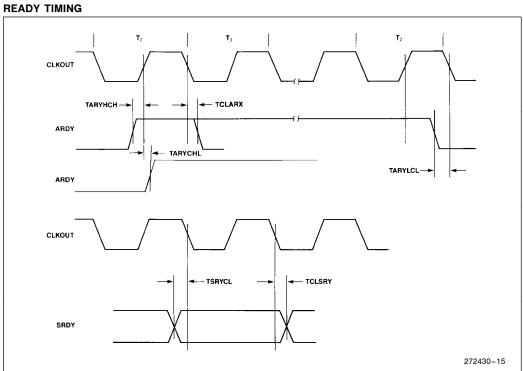

| READY Synchronization                                   |        | WAVEFORMS                     | 19   |

| LOCAL BUS CONTROLLER                                    | 9      | EXPRESS                       | 25   |

| Memory/Peripheral Control                               | 10     | EXECUTION TIMINGS             | 26   |

| Local Bus Arbitration<br>Local Bus Controller and Reset |        | INSTRUCTION SET SUMMARY       | 27   |

| PERIPHERAL ARCHITECTURE                                 | 10     | FOOTNOTES                     | 32   |

| Chip-Select/Ready Generation Lo                         | gic 10 | REVISION HISTORY              | 33   |

| DMA Channels                                            | 11     |                               |      |

| Timers                                                  | 11     |                               |      |

| Interrupt Controller                                    | 12     |                               |      |

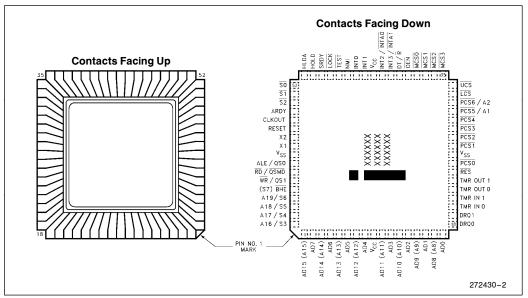

Figure 2. Ceramic Leadless Chip Carrier (JEDEC Type A)

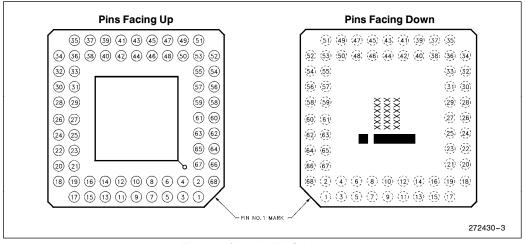

Figure 3. Ceramic Pin Grid Array

### NOTE:

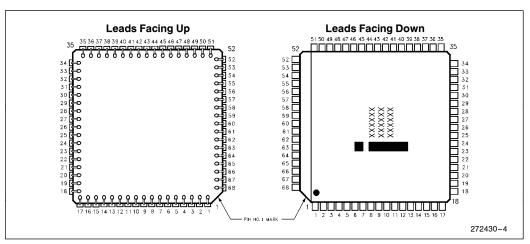

Figure 4. Plastic Leaded Chip Carrier

**Table 1. Pin Descriptions**

|                                                     | lable 1. Pin Descriptions |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------------------------------------------|---------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                              | No.                       | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| V <sub>CC</sub>                                     | 9<br>43                   | I      | SYSTEM POWER: +5 volt power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| V <sub>SS</sub>                                     | 26<br>60                  | I      | System Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| RESET                                               | 57                        | 0      | Reset Output indicates that the CPU is being reset, and can be used as a system reset. It is active HIGH, synchronized with the processor clock, and lasts an integer number of clock periods corresponding to the length of the RES signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

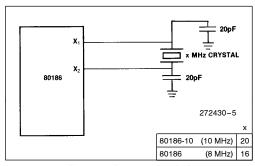

| X1<br>X2                                            | 59<br>58                  | 0      | Crystal Inputs X1 and X2 provide external connections for a fundamental mode parallel resonant crystal for the internal oscillator. Instead of using a crystal, an external clock may be applied to X1 while minimizing stray capacitance on X2. The input or oscillator frequency is internally divided by two to generate the clock signal (CLKOUT).                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| CLKOUT                                              | 56                        | 0      | Clock Output provides the system with a 50% duty cycle waveform. All device pin timings are specified relative to CLKOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| RES                                                 | 24                        | I      | An active $\overline{\text{RES}}$ causes the processor to immediately terminate its present activity, clear the internal logic, and enter a dormant state. This signal may be asynchronous to the processor clock. The processor begins fetching instructions approximately $6\frac{1}{2}$ clock cycles after $\overline{\text{RES}}$ is returned HIGH. For proper initialization, $V_{CC}$ must be within specifications and the clock signal must be stable for more than 4 clocks with $\overline{\text{RES}}$ held LOW. $\overline{\text{RES}}$ is internally synchronized. This input is provided with a Schmitt-trigger to facilitate power-on $\overline{\text{RES}}$ generation via an RC network. |  |  |  |  |  |  |

| TEST                                                | 47                        | 1/0    | TEST is examined by the WAIT instruction. If the TEST input is HIGH when "WAIT" execution begins, instruction execution will suspend. TEST will be resampled until it goes LOW, at which time execution will resume. If interrupts are enabled while the processor is waiting for TEST, interrupts will be serviced. During power-up, active RES is required to configure TEST as an input. This pin is synchronized internally.                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| TMR IN 0<br>TMR IN 1                                | 20<br>21                  | I<br>I | Timer Inputs are used either as clock or control signals, depending upon the programmed timer mode. These inputs are active HIGH (or LOW-to-HIGH transitions are counted) and internally synchronized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| TMR OUT 0<br>TMR OUT 1                              | 22<br>23                  | 0      | Timer outputs are used to provide single pulse or continous waveform generation, depending upon the timer mode selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| DRQ0<br>DRQ1                                        | 18<br>19                  | l<br>I | DMA Request is asserted HIGH by an external device when it is ready for DMA Channel 0 or 1 to perform a transfer. These signals are level-triggered and internally synchronized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| NMI                                                 | 46                        | I      | The Non-Maskable Interrupt input causes a Type 2 interrupt. An NMI transition from LOW to HIGH is latched and synchronized internally, and initiates the interrupt at the next instruction boundary. NMI must be asserted for at least one clock. The Non-Maskable Interrupt cannot be avoided by programming.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| INT0<br>INT1/SELECT<br>INT2/INTA0<br>INT3/INTA1/IRQ | 45<br>44<br>42<br>41      | <br>   | Maskable Interrupt Requests can be requested by activating one of these pins. When configured as inputs, these pins are active HIGH. Interrupt Requests are synchronized internally. INT2 and INT3 may be configured to provide active-LOW interrupt-acknowledge output signals. All interrupt inputs may be configured to be either edge- or level-triggered. To ensure recognition, all interrupt requests must remain active until the interrupt is acknowledged. When Slave Mode is selected, the function of these pins changes (see Interrupt Controller section of this data sheet).                                                                                                                |  |  |  |  |  |  |

Table 1. Pin Descriptions (Continued)

| A19/S6   65   O   Address Bus Outputs (16-19) and Bus Cycle Status (3-9) indicate the four most significant address bits during T1, These signals are active HIGH. During T2, T3, TW, and T4, the S6 pin is LOW to indicate a CPU-initiated bus cycle or HIGH to indicate a DMA-initiated bus cycle. During the same T-states, S3, S4, and S5 are always LOW. The status pins float during bus HOLD or RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol     | Symbol Pin Type Name and Function |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------|-----|----------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| A18/55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | No.                               |     | - ماطاء -            | o Due O                                                                   |                                                                                      |  |  |  |  |  |

| A17/S4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                   |     | I                    | • • • • • • • • • • • • • • • • • • • •                                   |                                                                                      |  |  |  |  |  |

| The status pins float during bus HOLD or RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                   |     | and T <sub>4</sub> , | the S6 p                                                                  | in is LOW to indicate a CPU-initiated bus cycle or HIGH to indicate a                |  |  |  |  |  |

| AD15 (A15)   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A16/S3     | 68                                | 0   |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD14 (A14)   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AD45 (A45) |                                   | 1/0 |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD13 (A12) 5 1/0 AD12 (A12) 7 7 AD12 (A12) 10 Includes byte of the data bus, pins D7 through D9, it is LOW during T1 when a byte is to be transferred onto the lower portion of the bus in memory or I/O operations. BHE does not exist on the 80188, as the data bus is only 8 bits wide.    AD14 (A10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD11 (A11)   10   1/0   AD10 (A10)   12   1/0   AD10 (A10)   12   1/0   AD8 (A8)   16   1/0   AD7   2   1/0   AD8 (A8)   16   1/0   AD8                                                      |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD10 (A10)   12   1/O   AD9 (A9)   14   1/O   AD7 (AP)   16   1/O   AD7 (AP)   16   1/O   AD7   2   1/O   AD6   A   1/O   AD7   2   1/O   AD8 (A8)   11   1/O   AD8 (A8)   11   1/O   AD8   AD8 (A8)   11   1/O   AD8   AD9                                                      | AD12 (A12) |                                   |     | I                    |                                                                           | · · · · · · · · · · · · · · · · · · ·                                                |  |  |  |  |  |

| AD9 (A9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                   |     | does no              | ot exist o                                                                | n the 80188, as the data bus is only 8 bits wide.                                    |  |  |  |  |  |

| ADB (A8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                   | 1/0 |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD4 AD3 11 1/O AD2 13 1/O AD1 15 1/O AD0 17 1/O  BHE/S7 (S7)  64 O  During T1 the Bus High Enable signal should be used to determine if data is to be enabled onto the most significant half of the data bus; pins D15-D8. BHE is LOW during T1 for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the higher half of the bus. The S7 status information is available during T2, T3, and T4, S7 is logically equivalent to BHE. BHE/S7 floats during HOLD. On the 80188, S7 is high during normal operation.  BHE and A0 Encodings (80186 Only)  ALE/QS0  ALE/QS0  ALE/QS0  61 O  Address Latch Enable/Queue Status 0 is provided by the processor to latch the address. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T1 of the associated bus cycle, effectively one-half clock cycle earlier than in the 8086. The trailing edge is generated off the CLKOUT rising edge in T1 as in the 8086. Note that ALE is never floated.  WRI/QS1  63 O  Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. WRI is active for T2, T3, and TW of any write cycle. It is active LOW, and floats during HOLD. When the processor is in queue status mode, the ALE/QS0 and WRI/QS1 pins provide information about processor/instruction queue interaction.  GS1 QS0 Queue Operation  0 0 No queue Operation  1 1 Subsequent byte fetched from the queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| AD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| ADO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| BHE/S7 (S7)   64   O   During T <sub>1</sub> the Bus High Enable signal should be used to determine if data is to be enabled onto the most significant half of the data bus; pins D <sub>15</sub> -D <sub>8</sub> . BHE is LOW during T <sub>1</sub> for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the higher half of the bus. The S <sub>7</sub> status information is available during T <sub>2</sub> , T <sub>3</sub> , and T <sub>4</sub> . S <sub>7</sub> is logically equivalent to BHE. BHE/S7 floats during HOLD. On the 80188, S7 is high during normal operation.    BHE   A0   Value   Punction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1          |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| enabled onto the most significant half of the data bus; pins D <sub>15</sub> -D <sub>8</sub> . BHE is LOW during T <sub>1</sub> for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the higher half of the bus. The S <sub>7</sub> status information is available during T <sub>2</sub> , T <sub>3</sub> , and T <sub>4</sub> . S <sub>7</sub> is logically equivalent to BHE. BHE/S7 floats during HOLD. On the 80188, S7 is high during normal operation.    BHE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u> </u>   |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| during T <sub>1</sub> for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the higher half of the bus. The S <sub>7</sub> status information is available during T <sub>2</sub> , T <sub>3</sub> , and T <sub>4</sub> . S <sub>7</sub> is logically equivalent to BHE. BHE/S7 floats during HOLD. On the 80188, S7 is high during normal operation.    BHE and A0 Encodings (80186 Only)   BHE A0 Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | 64                                | 0   |                      |                                                                           |                                                                                      |  |  |  |  |  |

| transferred on the higher half of the bus. The S <sub>7</sub> status information is available during T <sub>2</sub> , T <sub>3</sub> , and T <sub>4</sub> , S <sub>7</sub> is logically equivalent to BHE. BHE/S7 floats during HOLD. On the 80188, S7 is high during normal operation.    BHE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (57)       |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| BHE   A0   Value   Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                   |     | transfe              | rred on th                                                                | ne higher half of the bus. The S <sub>7</sub> status information is available during |  |  |  |  |  |

| BHE   A0   Value   Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| BHE   Value   Value   Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                   |     | 00100,               | 07 13 1119                                                                |                                                                                      |  |  |  |  |  |

| ALE/QS0  61  O Word Transfer 0 ltyle Transfer on upper half of data bus (D15–D8) Byte Transfer on lower half of data bus (D7–D0) Reserved  ALE/QS0  61  O Address Latch Enable/Queue Status 0 is provided by the processor to latch the address. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T1 of the associated bus cycle, effectively one-half clock cycle earlier than in the 8086. Note that ALE is never floated.  WR/QS1  63  O Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. WR is active for T2, T3, and TW of any write cycle. It is active LOW, and floats during HOLD. When the processor is in queue status mode, the ALE/QS0 and WR/QS1 pins provide information about processor/instruction queue interaction.  QS1  QS0  Queue Operation  No queue operation  First opcode byte fetched from the queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| ALE/QS0   61   O   Address Latch Enable/Queue Status 0 is provided by the processor to latch the address. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T <sub>1</sub> of the associated bus cycle, effectively one-half clock cycle earlier than in the 8086. The trailing edge is generated off the CLKOUT rising edge in T <sub>1</sub> as in the 8086. Note that ALE is never floated.    With Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. WR is active for T <sub>2</sub> , T <sub>3</sub> , and T <sub>W</sub> of any write cycle. It is active LOW, and floats during HOLD. When the processor is in queue status mode, the ALE/QS0 and WR/QS1 pins provide information about processor/instruction queue interaction.    QS1   QS0   Queue Operation   Queue Operation   O No queue operation   First opcode byte fetched from the queue   Operation   Operat |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

| ALE/QS0  61  O Address Latch Enable/Queue Status 0 is provided by the processor to latch the address. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T <sub>1</sub> of the associated bus cycle, effectively one-half clock cycle earlier than in the 8086. The trailing edge is generated off the CLKOUT rising edge in T <sub>1</sub> as in the 8086. Note that ALE is never floated.  WR/QS1  63  O Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. WR is active for T <sub>2</sub> , T <sub>3</sub> , and T <sub>W</sub> of any write cycle. It is active LOW, and floats during HOLD. When the processor is in queue status mode, the ALE/QS0 and WR/QS1 pins provide information about processor/instruction queue interaction.  QS1  QS0  Queue Operation  0  No queue operation  0  1  First opcode byte fetched from the queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                   |     |                      |                                                                           |                                                                                      |  |  |  |  |  |

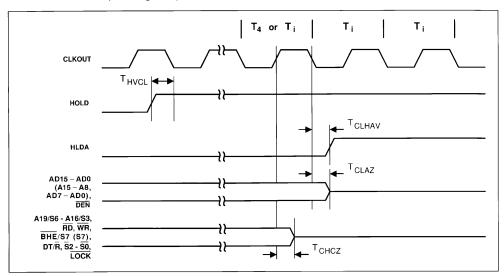

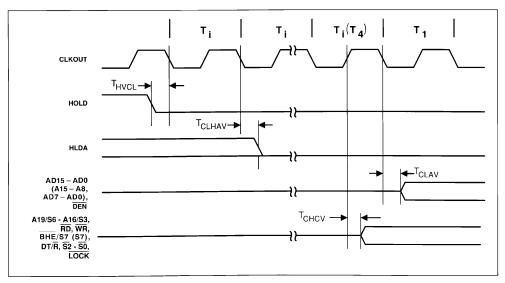

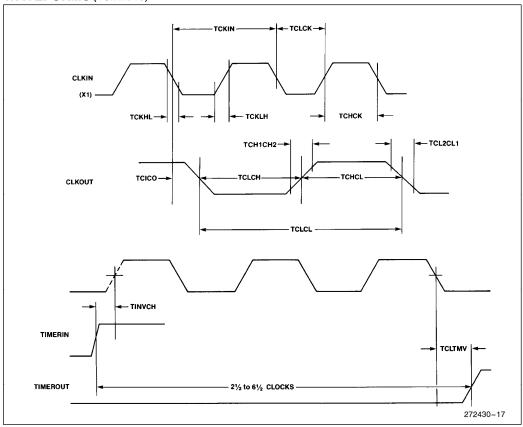

| ALE/QS0  61  O Address Latch Enable/Queue Status 0 is provided by the processor to latch the address. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T <sub>1</sub> of the associated bus cycle, effectively one-half clock cycle earlier than in the 8086. The trailing edge is generated off the CLKOUT rising edge in T <sub>1</sub> as in the 8086. Note that ALE is never floated.  WR/QS1  63  O Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. WR is active for T <sub>2</sub> , T <sub>3</sub> , and T <sub>W</sub> of any write cycle. It is active LOW, and floats during HOLD. When the processor is in queue status mode, the ALE/QS0 and WR/QS1 pins provide information about processor/instruction queue interaction.  QS1  QS0  Queue Operation  0  No queue operation  1  Subsequent byte fetched from the queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                   |     | l                    |                                                                           |                                                                                      |  |  |  |  |  |