PCjs Machines

Home of the original IBM PC emulator for browsers.

Texas Instruments TI-57 U.S. Patent No. 4,125,901

US4125901

TABLE OF CONTENTS

- Related Patents and Applications

- Background of the Invention

- Brief Description of the Drawings

- Detailed Description of Specific Embodiment

- Detailed Description of System Logic Diagram

- The ROM and Program Counter

- The Subroutine Stack

- The Branch Logic and Condition Latch

- The Test Circuitry

- The Instruction Word Decoder Logic

- Register Address Buffer

- Storage Register Input/Output Circuit

- The Operational Register Selector Gates

- Arithmetic Unit

- Register R5

- Scan Generator Counter and Segment/Keyboard Scan

- Keyboard Logic

- Display Decoder

- Output Register

- State Time Generator

- Register Configuration

CLAIMS

What is claimed is:

- An arithmetic unit and memory system for an electronic microprocessor comprising: (a) a plurality of operational registers, each of said operational registers having an input and first and second outputs, (b) an arithmetic unit having two inputs and an output and having means for performing arithmetic operations on data received at the inputs thereof and for communicating the results of said arithmetic operations to the output thereof, and (c) a plurality of operational register selector gates interconnecting said plurality of operational registers and said arithmetic unit for connecting a selected one of said first and second outputs of a selected one of said operational registers to one of the inputs of said arithmetic unit.

- The system according to claim 1, further including means for connecting the output of said arithmetic unit to a selected one of said plurality of operational registers.

- The system according to claim 2, wherein said plurality of operational register selector gates comprises: (a) first gating means for selectively coupling the outputs of said operational registers to a first input of said arithmetic unit, and (b) second gating means for selectively connecting the outputs of said operational registers to a second input of said arithmetic unit.

- A system according to claim 3, wherein said first and second gating means include first means for selectively coupling the first and second outputs of said operational registers to a common point associated with each one of said operational registers and second means for interconnecting said common points with the first and second inputs of said arithmetic unit.

- The system according to claim 4, wherein said second means includes a plurality of single transistors coupling the common point for each operational register to the first input of said arithmetic unit and another plurality of single transistors coupling the common point for each operational register to the second input of said arithmetic unit.

- The system as defined in claim 5, wherein said first means includes a plurality of single transistors each coupling the first output of said plurality of registers to the common point associated with said registers and another plurality of single transistors each coupling the second output of said plurality of registers to the common point associated with said registers.

- In an electronic microprocessor having a memory for storing a plurality of instruction words, means for outputting the instruction words stored in said memory, a plurality of operational registers for storing numeric data, each said operational register having an input and a first output, an arithmetic unit for performing arithmetic operations on the numeric data stored in said operational registers, decoder means for decoding the instruction words outputted from said memory, and a plurality of register selector gates, responsive to said decoder means, for communicating the numeric data stored in said operational registers to said arithmetic unit, the improvement comprising a second output associated with each of said operational registers for use during left hand shifting of data stored in said operational registers and wherein said operational register selector gates include first gating means for selectively coupling the first and second outputs of said operational registers to a common point associated with each one of said operational registers and second gating means for selectively coupling said common points with said arithmetic unit.

- The microprocessor according to claim 7, wherein said arithmetic unit has first and second inputs, wherein said second gating means comprises a first plurality of transistors coupling the common point for each operational register to the first input of said arithmetic unit and a second plurality of transistors coupling the common point for each operational register to the second input of said arithmetic unit.

- An arithmetic unit and memory system for an electronic microprocessor comprising: (a) a plurality of operational registers, each of said operational registers having an input and two outputs; (b) an arithmetic unit; (c) first gating means for selectively coupling the two outputs of said operational registers to common points associated with each one of said operational registers; and (d) second gating means selectively coupling said common points and said arithmetic unit.

- The arithmetic unit and memory system according to claim 9, wherein said first gating means comprises a first plurality of single transistors each coupling a first one of the two outputs of said operational registers to the common point associated with said operational registers and a second plurality of single transistors each coupling a second one of the two outputs of said operational registers to the common point associated with said operational registers.

- The arithmetic unit and memory system according to claim 9, wherein each of said operational registers comprises a multi-stage shift register including an input stage and an output stage and wherein one of the two outputs from each operational register is provided by the output stage of the shift register and the other of the two outputs from each operational register is provided by another stage of the shift register.

- The arithmetic unit and memory system according to claim 9, wherein said arithmetic unit has first and second inputs and wherein said second gating means includes first means for selectively coupling the common points of said operational registers to said first input of said arithmetic unit and second means for selectively coupling the common points of said operational registers to said second input of said arithmetic unit.

- The arithmetic unit and memory system according to claim 12, wherein said first means comprises a first plurality of single transistors, each of which couples one of said common points to the first input of said arithmetic unit and wherein said second means comprises a second plurality of single transistors each of which couples one of said common points to the second input of said arithmetic unit.

RELATED PATENTS AND APPLICATIONS

Patents and copending applications related to this patent include:

- Electronic Calculator or Microprocessor System Having Combined Data and Flag Bit Storage System, Ser. No. 736,271, filed Oct. 27, 1976;

- Electronic Calculator Power Up Clear System, Ser. No. 736,273, filed Oct. 27, 1976;

- Two Speed Shift Register For Electronic Calculator Or Microprocessor System, U.S. Pat. No. 4,079,459;

- Data Display System For Electronic Calculator or Microprocessor, Ser. No. 736,274, filed Oct. 27, 1976;

- Synchronous State Counter, Ser. No. 735,918, filed Oct. 27, 1976;

- Electronic Calculator Or Microprocessor System Having A Hexadecimal/Binary Coded Decimal Arithmetic Unit Ser. No. 736,005, filed Oct. 27, 1976;

- Electronic Calculator With Indirect Addressing, Ser. No. 736,001, filed Oct. 27, 1976;

- Electronic Calculator Or Microprocessor With Mask Logic Effective During Data Exchange Operation, U.S. Pat. No. 4,078,251;

- Non-Sequential Counter, Ser. No. 735,917, filed Oct. 27, 1976; and

- Electronic Calculator Or Microprocessor System Having Phase Multiplexed Serial Shift Registers For Storing Data, Ser. No. 747,279, filed Dec. 3, 1976.

BACKGROUND OF THE INVENTION

Electronic calculator systems of the type wherein all of the main electronic functions are integrated in a single large cell integrated semiconductor chip or in a small number of such chips, are described in the following U.S. Patents, which are assigned the assignee of this invention:

U.s. pat. No. 3,919,532 issued to Michael J. Cochran and Charles P. Grant on Nov. 11, 1975 and entitled “CALCULATOR SYSTEM HAVING AN EXCHANGE DATA MEMORY REGISTER”.

U.s. pat. No. 3,934,233 issued to Roger J. Fisher and Gerald D. Rogers on Jan. 20, 1976 and entitled “READ-ONLY-MEMORY FOR ELECTRONIC CALCULATOR”.

U.s. pat. No. 3,931,507 issued Jan. 6, 1976 to George L. Brantingham entitled “POWER-UP CLEAR IN AN ELECTRONIC DIGITAL CALCULATOR”.

The concepts of these prior applications have made possible vast reductions in the cost of small personal-size calculators. Continuing efforts to reduce the cost of these products include the design of a single chip calculator system for use in large capacity calculators, such as scientific or business calculators. The chip disclosed herein may be utilized in scientific or business calculators for instance, because this chip has provisions for a number of storage registers, in addition to operational registers, as well as sufficient capacity to solve the more complicated mathematical expressions and functions used in scientific and business calculators including, for example, trigonometric and logarithmic relationships.

The present invention relates to an arithmetic unit and memory system for an electronic calculator or microprocessor. An entire electronic calculator system including the arithmetic unit and memory system of this invention is disclosed. The electronic calculator disclosed is a serial, word organized calculator; however, the invention disclosed is not limited to that type calculator. In the prior art, such as that exemplified by the calculator disclosed in U.S. Pat. No. 3,919,532, a plurality of AND and OR logic gates have been utilized for transferring data between the operational registers and the arithmetic unit of a calculator. Further the logic gates were arranged such that only particular pairs of the operational registers could be inputted to the arithmetic unit at the same time.

It was one object of this invention therefore to provide register selector gates interconnecting the calculator memory, i.e., the calculators operational registers, with the inputs of the arithmetic unit. It was another object of this invention to permit this data stored in any two of the operational registers to be inputted to the arithmetic unit at the same time.

It is yet another object of this invention to permit the data outputted from the arithmetic unit to be inputted to a selected one of either of the two registers providing inputs to the arithmetic unit. It is still another object of this invention to simplify the register selector gates by using MOS transfer gates for interconnecting the operational registers with the inputs of the adder as opposed to using the more complex AND and OR logic gates of the prior art.

The foregoing objects are achieved according to the present invention as is now described. In a preferred embodiment of the invention, an arithmetic unit and memory system including a plurality of selector gates are implemented on a seimconductor chip. The memory preferably comprises a plurality of operational registers and the arithmetic unit preferably has two inputs and an output and performs arithmetic operations on data received at the inputs and communicates the results thereof to the output. The operational registers and the inputs of the arithmetic unit are interconnected by a plurality of operational register selector gates arranged to permit any selected two of the plurality of operational registers to be connected to the input of the arithmetic unit. Further, additional selector gates are preferably provided for interconnecting the output of the arithmetic unit with a selected one of the operational registers connected to the inputs of the arithmetic unit. Still further, in a preferred embodiment of the invention, the aforementioned selector gates comprised simple MOS transfer gates as opposed to more complex AND/or OR logic gates.

BRIEF DESCRIPTION OF THE DRAWINGS

The novel features believed characteristic of the invention are set forth in the appended claims. The invention itself, however, as well as a preferred mode of use, further objects and advantages thereof, will be best understood by reference to the following detailed description of an illustrative embodiment when read in conjunction with the accompanying drawings, wherein:

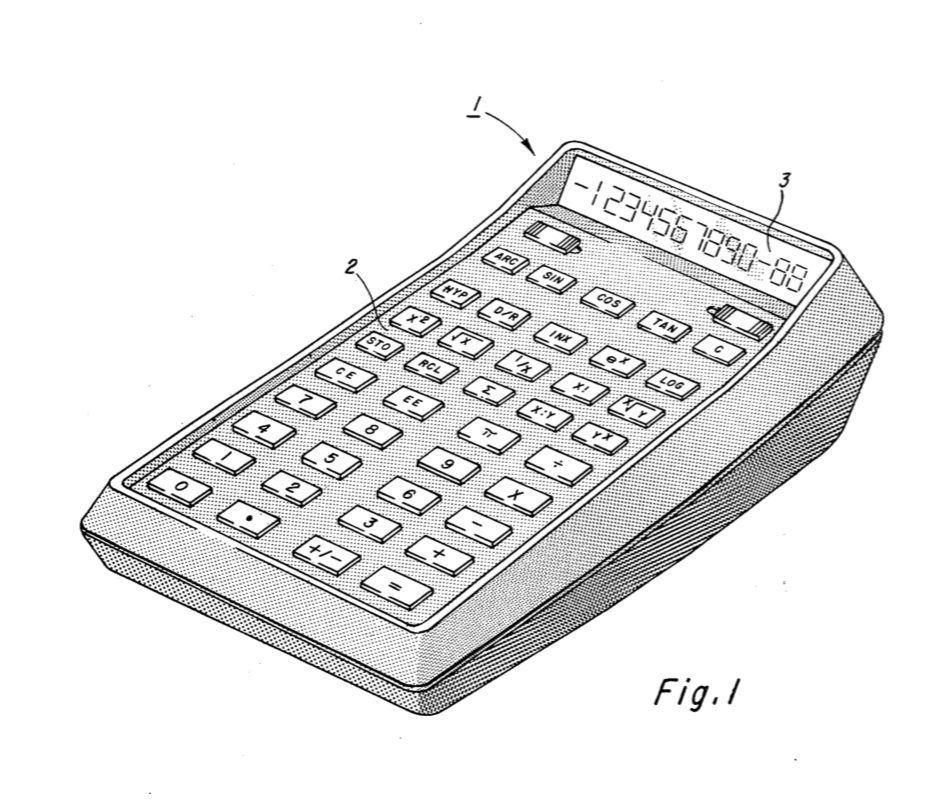

FIG. 1 is a pictorial view of a portable, electronic, hand-held calculator of the type which may embody the present invention;

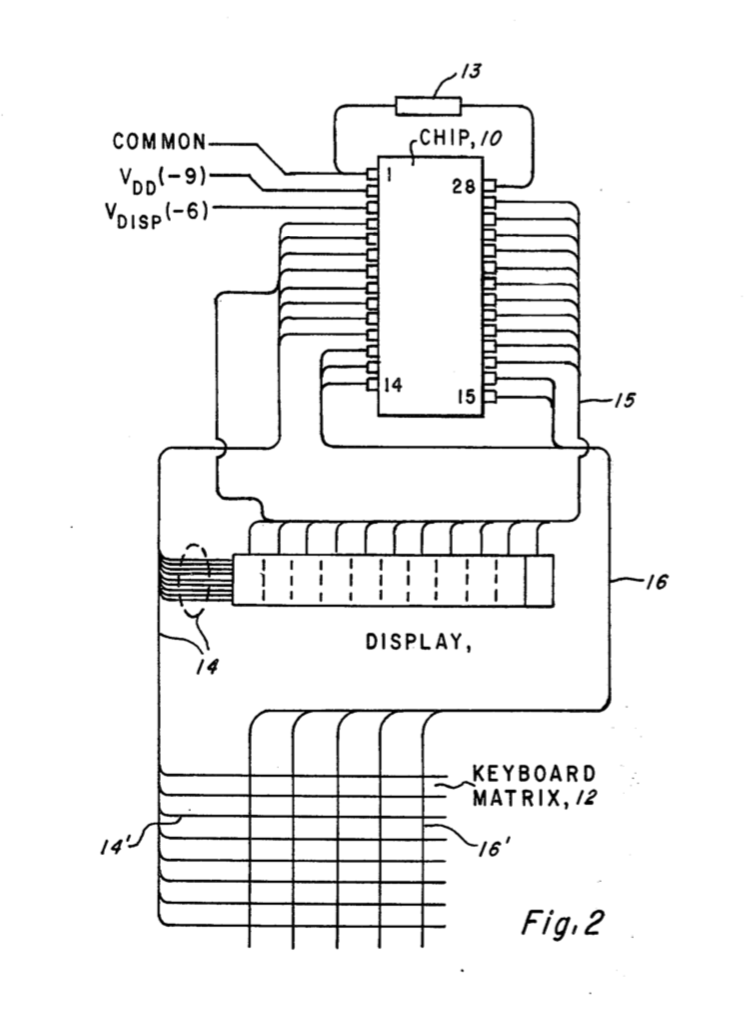

FIG. 2 is a functional schematic diagram of a single chip calculator system of the type which may embody the present invention;

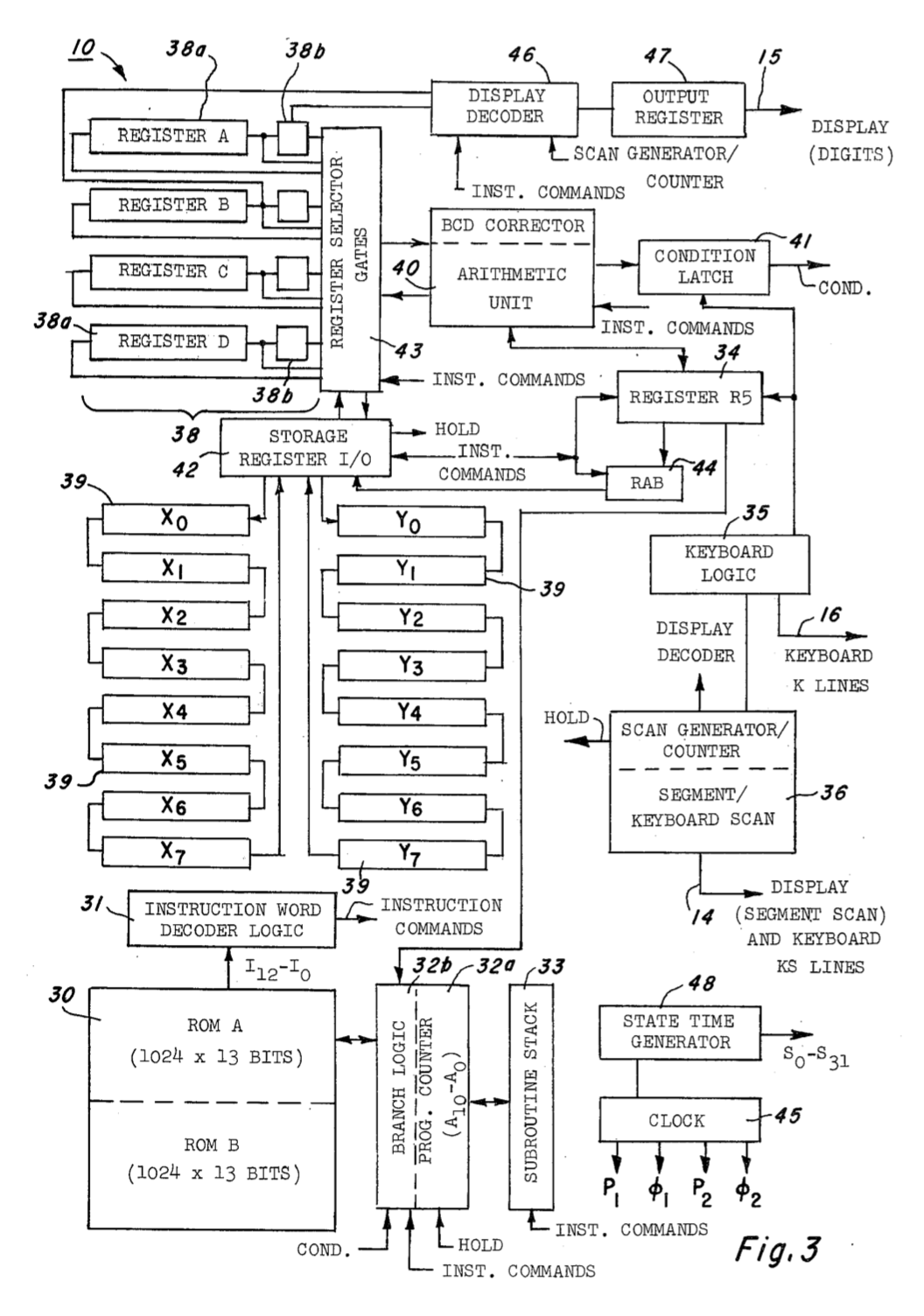

FIG. 3 depicts a functional block diagram of the single chip calculator system embodying the present invention;

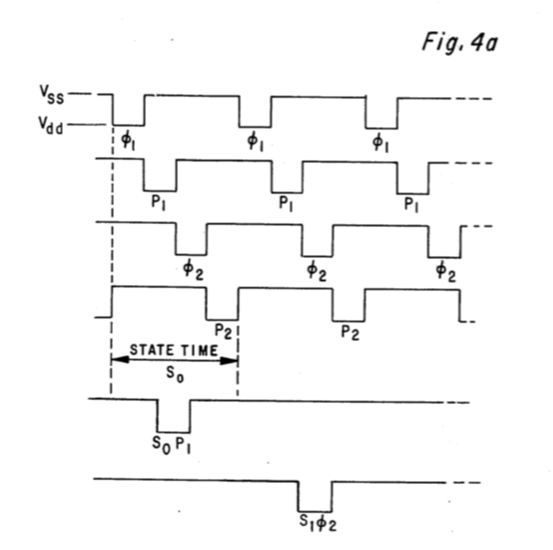

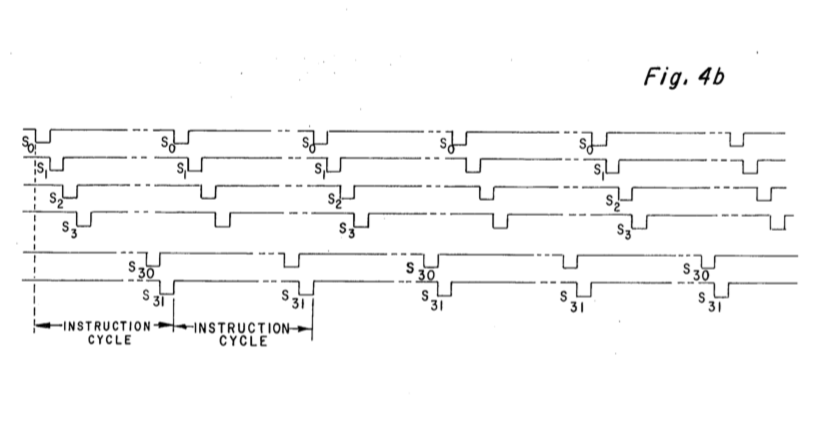

FIGS. 4(a) and 4(b) depict the timing signals generated by a clock implemented in the calculator system, the timing signals being shown in representative form;

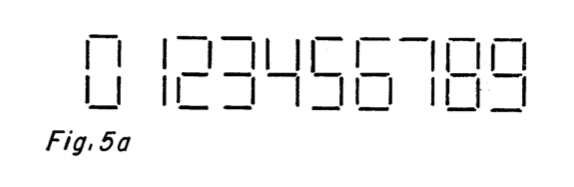

FIGS. 5(a) and 5(b) depict a segmented display and a manner in which a calculator system may be interconnected therewith;

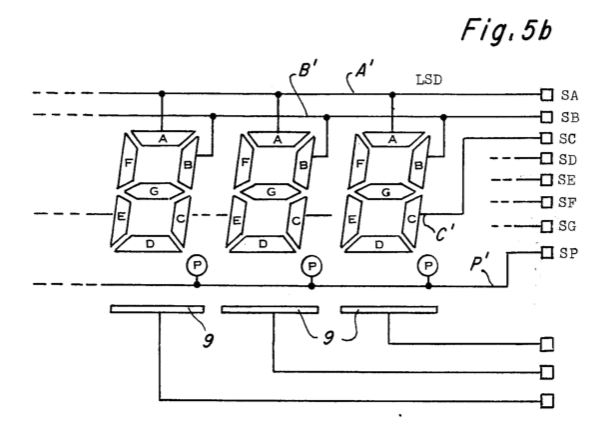

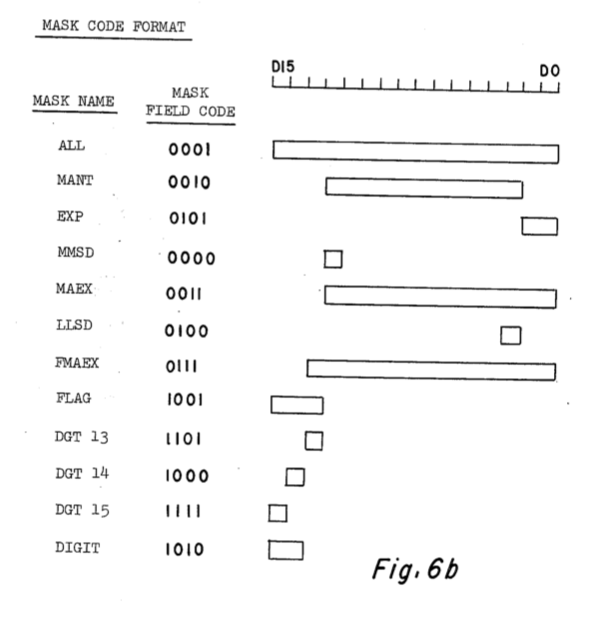

FIGS. 6(a) and 6(b) depict the format of the data word stored in the operational and storage registers of the calculator system, the MASK codes which are used in the instruction words implemented in the read-only-memory and how these various masks relate to the data words;

FIGS. 7(a)-7(c) form a logic diagram of the program counter, the branch logic, the test circuitry, the subroutine stack and the read-only-memory of the calculator system;

FIGS. 8(a)-8(i) form a logic diagram of the instruction word decoder logic; the operational registers, the storage registers, the register address buffer, and the counter associated with the storage registers;

FIG. 9 is a logic diagram of the operational register selector gates;

FIGS. 10(a)-10(d) form a logic diagram of the arithmetic unit and the R5 register;

FIGS. 11(a)-11(f) form a logic diagram of segment/keyboard scan and scan generator counter, keyboard logic, display decoder, output register and state time generator;

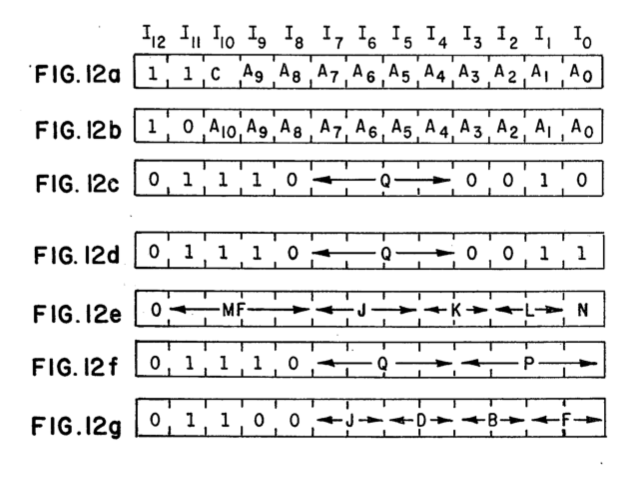

FIGS. 12(a)-12(g) depict the format of various instruction words described in Table I;

FIG. 13 is a logic diagram of circuits used to interconnect the test circuitry of FIG. 7 with the K1-K4 keyboard line pins of FIG. 11; and

FIG. 14 depicts alternate embodiments of register architecture for the operational and storage registers of the system.

DETAILED DESCRIPTION OF SPECIFIC EMBODIMENT

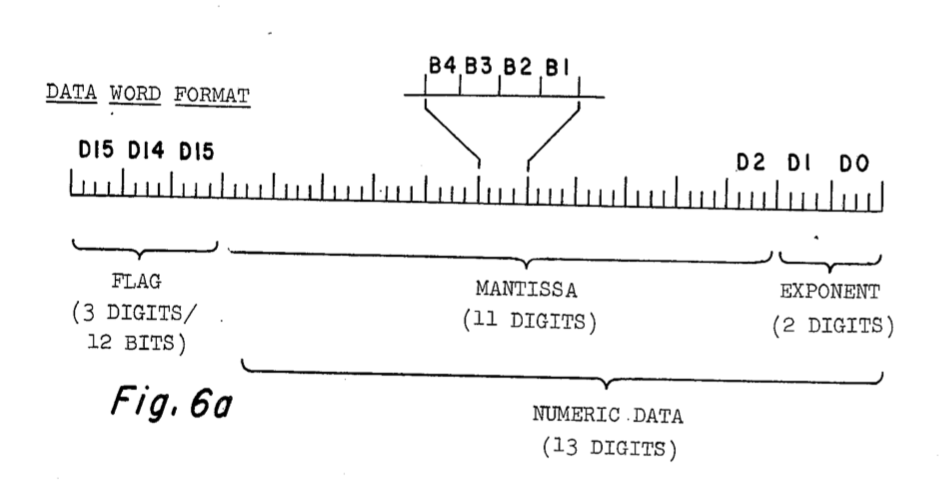

Referring to FIG. 1, an electronic portable calculator the type which may employ features of this invention is shown in pictorial form. The calculator 1 comprises the keyboard 2 and the display 3. The display 3, in one embodiment, consists of twelve digits or characters, each provided by an array of light-emitting diodes, a vacuum fluorescent tube, liquid crystal devices or other display means. The display is preferably implemented having eight mantissa digits, two exponent digits, and two annotator places for signs, et cetera (one place for the mantissa and one place for the exponent), thereby permitting outputting of data in scientific notation. Ordinarily, the display would be of the seven segment or eight segment variety, with provision for indicating a decimal point for each digit. The keyboard 2 or other such input means preferably includes a set of number keys (0-9), a decimal point key, a plurality of function command keys including, for example, exponential, logarithm and trigonometrical functions. The exponential and logarithmic function command keys include, for example, X2, the square root of X, the reciprocal of X, eX, the common log of X, and the natural log of X. The trigonometrical functions include for instance the sine, cosine, tangent and their inverses, the hyperbolic sine, hyperbolic cosine, and hyperbolic tangent of X and inverse hyperbolic functions. Other function command keys include store (STO), and recall (RCL), keys for respectively storing and recalling a number stored in one of the memory or storage registers implemented on the chip. The enter exponent key (EE) allows exponent entry of the number displayed in scientific notation. A plus/minus key is provided for changing the sign of the display number. An exchange key (X:Y) is provided for exchanging operator and operand of an arithmetic function. More conventional function command keys are supplied, including the clear key (C), the clear entry key (CE), and the plus (+ ), minus (-), multiply (×), divide (÷), and equal (=) keys.

Referring now to FIG. 2 there is shown a functional schematic diagram of the single chip calculator system. A single chip 10 is shown here in a standard twenty-eight pin dual-in-line package; however, it is to be understood that how the chip 10 is shown as being interconnected with a twelve-character display 11 utilizing a segment scan technique. Each of the 7 segments of the character plus the decimal point for each character position are individually connected in common to the segment scan conductors 14. An individual common lead for each character position is connected by bus 15 to chip 10. The details of segment scanning are explained with reference to FIGS. 3 and 5 and it should be evident to one trained in the art that the number of segments selected and the number of characters selected is a design choice.

Chip 10 is interconnected with an X/Y matrix keyboard 12 utilizing five column conductors 16’ and eight row conductors 14’, the row conductors 14’ being individually connected to the segment scan conductors 14 and the column conductors 16’ being individually connected via bus 16 to chip 10. An X/Y matrix keyboard having five column conductors 16’ and eight row conductors 14’ may accommodate up to 40 switches located at the intersections of the conductors; however, the number of conductors 14’ and 16’ and consequently the number of switches is a design choice. The chip 10 is further connected to a source of DC electrical power through a common connection (Vss) at pin 1, a Vdd connection at pin 2, and a VDISP connection at pin 3 for the display. Further, a resistor 13 is connected between pins 28 and 1 as a means of controlling the chip’s oscillator frequency. External resistor 13 could of course be implemented on chip 10, however, resistor 13 is preferably implemented off chip 10 in order to be able to “fine tune” the frequency of the clock oscillator implemented on chip 10.

Referring now to FIG. 3 there is shown a functional block diagram of the single chip calculator system of this invention showing various circuits implemented on chip 10. A detailed description of the individual function blocks will be discussed subsequently with regard to FIGS. 7, 8, 9, 10 and 11, with only a general functional description of the basic system here set forth. It is to be understood that on the block diagram of FIG. 3, a connection represented by a single line may represent a plurality of actual hardware interconnections, and for ease and simplicity of illustration, a single line may represent a plurality of different functions. The calculator system of this invention includes on chip 10 a main program read-only-memory (ROM) 30, preferably having two sections which may be referred to as ROM A and ROM B. The reason for denoting that ROM 30 has two sections will be subsequently explained in regard to the instruction words implementable in ROM 30. Main program ROM 30 is responsive to an eleven bit ROM address (A10 -A0) stored in program counter 32a and produces, in response thereto, a thirteen bit instruction word (I12 -I0), which is provided to instruction word decoder logic 31. Instruction word decoder logic 31 interprets the instruction word received from ROM 30 and produces in response thereto a plurality of command signals to the other circuits implemented on chip 10. These command signals direct how data is transferred within chip 10, how the data is manipulated by arithmetic unit 40 and serves several other functions which will be explained with reference to the circuits receiving the command signals.

Program counter circuit 32a includes an add-one circuit and is associated with branch logic 32b. The add-one circuit in program counter 32a increments the ROM address stored in the address register in program counter 32a by adding the number one to the address stored in the address register during each instruction cycle, thereby causing the instruction words stored in ROM 30 to be read out sequentially. At times, however, it is advantageous to be able to execute the same instruction word repetitively and therefore the add-one circuit in program counter 32a is responsive to a HOLD command which disables the add-one circuit allowing the address stored in program counter 32a to remain unchanged. Branch logic 32b is responsive to commands generated by instruction word decoder logic 31 for inserting a new ROM address in program counter 32a, thereby permitting the program stored in ROM 30 to “branch” to a new location in ROM 30 rather than cycling sequentially through the instruction words stored in ROM 30. As will be seen with respect to the discussion of the instruction word set and the details of the branch logic 32b and program counter 32a circuits, a branch instruction received from instruction word decoder logic 31 may be either a conditional or an unconditional branch. If unconditional, the branch automatically occurs. If conditional, however, the branch instruction is executed only if the state of the condition latch 41 matches the state of a selected bit in the conditional branch instruction. If a match does not occur, program counter 32a merely cycles to the next sequential ROM address. Thus, branch logic 32b and program counter 32a circuits are interfaced with condition latch 41.

If a branch is to be accomplished, the program counter must be updated with the new ROM address by branch logic 32b. This new ROM address is typically derived from the branch instruction, but as will be seen from the discussion regarding the instruction word set, the new ROM address may also be derived from an address stored in an auxiliary register called R5 register 34. Since R5 register 34 can be loaded with an address corresponding the depression of a particular switch or key on keyboard matrix 12 (FIG. 2) or with number from an operational register 38 supplied via arithmetic unit 40, the new ROM address can be made dependent on the particular keyboard key depressed or can be an “indirect” address generated in one of the operational registers.

Branch logic and program counter circuit 32 is further interconnected with a subroutine stack 33. Subroutine stack 33 is preferably a three level stack having eleven bits per level which receives an incremented ROM address from program counter 32a in response to an unconditional branch command (CALL) and supplies the most recently received ROM address back to program counter 32a in response to a RETURN command received from instruction word decoder logic 31. The ROM address loaded into subroutine stack 33 in response to an unconditional branch command is the incremented address to which program counter 32a would have otherwise cycled. Therefore, when an unconditional branch instruction is encountered in ROM 30, program counter 32a is caused to branch to the address specified by the unconditional branch command and then increments that address by one each instruction cycle until another branch or a return command is received. When a return command is encountered, the most recently stored address in subroutine stack 33 is loaded back into program counter 32a, thus the addressing of the program stored in ROM 30 “returns” to the instruction address following the last unconditional branch instruction word location. Since subroutine stack 33 is a three level stack, three levels of subroutining are possible. Should a fourth address be loaded into subroutine stack 33, the first stored address is lost and only the second through fourth addresses will remain in subroutines stack 33.

R5 register 34 is an eight bit register which stores the two least significant digits generated by arithmetic unit 40 unless keyboard logic 35 in combination with a keyboard scan circuit in the scan generator/counter 36 indicates that one of the calculator keyboard keys has been depressed, in which case, an address associated with the key depressed is loaded into R5 register 34. The keyboard key address loaded into R5 register 34 may then be loaded into program counter 32a upon a “Branch on R5” instruction command, thereby permitting the keyboard to address ROM 30. Alternatively, a “branch on R5” instruction command may be utilized to perform indirect addressing by using the contents of one or two of the operational registers 38, as aforementioned. Since program counter 32a is an eleven bit counter, the three most significant bits (MSB’s) are loaded with zeros when the eight bit address from R5 register 34 is loaded into program counter 32a.

Referring briefly to FIG. 6a, the format of the data stored in the various operational and storage registers implemented on chip 10 is depicted along with the effect of the various mask codes used in many instruction words. With respect to the format of the data, it can be seen that there are sixteen digits (D0-D15) in a data word; preferably, the three most significant digits (MSD’s) provide twelve flag bits and the thirteen least significant digits (LSD’s) provide thirteen digits for numeric data. However, as will be seen, the calculator system disclosed has sufficient flexibility to permit the three MSD’s to be used either partially or totally for data storage in addition to the thirteen LSD’s, if desired during certain operations. Whether the calculator is operating in hexadecimal or binary coded deciman (BCD), four binary bits are required to represent each digit. The data word is serially organized, so each data word comprises 64 (e.g. 16 × 4) binary bits.

Referring again to FIG. 3, chip 10 is provided with four operational registers (register A-D) 38 and sixteen data storage registers (X0 -X7 and Y0 -Y7) 39. The operational registers 38 and the storage registers 39 are each 64 bit shift registers, accommodating the 64 bit format of the data words. The sixteen data storage registers 39 are separated into X and Y groups, each group comprising eight serially connected registers, thus each group of eight registers may be viewed as a 512 (e.g. 64 × 8) bit shift register. Both groups of shift registers are interconnected with storage register input-output (I/O) circuit 42. The first bit clocked out of a storage register 39 is the least significant bit of digit D0.

The operational registers 38 are similarly 64 bit registers, the 38a portion having sixty bits of capacity and the 38b portions having four bits of capacity. The operational registers 38, including the point of junction between 38a and 38b portions, are interconnected with a plurality of register selector gates 43 which control the exchange of data between the operational registers and with arithmetic unit 40. As will be subsequently discussed in greater detail, the separation of operational registers A-D 38 into the aforementioned sixty bit and four bit portions and the connection therebetween with register selector gates 43, facilitates right or left shifting of data, because then it is desirable for the register selector gates 43 to be able to selectively pick off the data word starting with the D15 digit, which is stored in portion 38b or the D0 digit, which is stored in portion 38a at the beginning of an instruction cycle (state S0) for instance. Storage register I/O circuit 42 is interconnected with register A to permit movement of a data word between a selected storage register 39 and operational register A.

A data word may be either outputted from Register A 38 and stored in a selected storage register and stored in Register A. To effect such movement of a data word between Register A and a selected storage register 39, an appropriate instruction word from ROM 30 is received by instruction word decoder logic 31 indicating (1) from which group, X or Y, the particular storage register 39 is to be selected and (2) whether the data word is being moved from Register A to a storage register or from a storage register to Register A. The contents of an address register, register address buffer (RAB) 44, indicates which one of the eight storage registers in the addressed group is being selected.

RAB 44 is a three bit address register which can be loaded either from R5 register (three least significant bits) or from three selected bits of an instruction word as directed by appropriate instruction commands. The data words stored in the eight storage registers 39 in each group normally recirculate, with each 64 bit data word moving to an adjacent storage register location during each instruction cycle. Thus, during one instruction cycle the contents of X0 shifts to X1 while the contents of X1 shifts to X2 and so forth. This shifting, of course, is responsive to the outputs from clock 45. Storage register I/O circuit 42 further includes a three bit counter which is likewise responsive to clock generator 45 for indicating which one of the eight data words stored in the addressed group is ready to be read out of X7 or Y7. Thus the three bit counter implemented in storage register I/O circuit 42 increments by one each instruction cycle. When a data word is to be read from or into a selected storage register 39, RAB 44 is first loaded with a three bit binary number indicating which one of the eight data word locations in a group is to be addressed. Then an instruction word is decoded by instruction word decoder logic 31 commanding storage register I/O circuit 42 to select the proper group, X or Y, and to count instruction cycles until the counter contained therein matches the state of RAB 44. Thus it can be seen that it could require up to seven instruction cycles for the selected data word in one of the groups, X or Y, to be shifted into a position preparatory to reading out of or into that group. Thus storage register I/O circuit 42 generates the HOLD command which inhibits incrementing program counter 32 until the counter in storage register I/O circuit 42 matches the state of RAB 44 and the desired data is moved between the appropriate group and Register A.

Arithmetic unit 40 is a serially organized arithmetic unit which includes a binary coded decimal (BCD) corrector. The BCD corrector may be disabled by an appropriate instruction command thereby permitting arithmetic unit 40 to operate either in hexadecimal base or in binary coded decimal base, as desired. As aforementioned, the data format preferably includes twelve flag bits. These flag bits are used, for instance, during many problems for keeping tract of the results of certain logical operations. Including the flag bits in the data words stored in the operational registers 38A and 38B and in the storage registers 39 is an important feature of this invention which permits greater programming flexibility in implementing the instruction words into ROM 30 and further simplifies chip 10 in that it eliminates the need for the discrete or dedicated flag registers or latches used in the prior art, and permits the flags to be processed in arithmetic unit 40 rather than in separate flag logic circuitry as done in the prior art. Arithmetic unit 40 is responsive to selected flag bits and selected instruction commands (Table I, Section 7) for setting the condition latch 41. Thus, in accordance with selected instruction words (Table I, Section 7), the twelve flags may be individually set, reset, toggled, or tested. Further, the three MSD’s used for flags may be arithmetically operated upon in hexadecimal using appropriate instruction words (see Table I) with appropriate flag masks (see FIG. 6).

The “set flag” instruction (see Table I, Section 7) loads a binary one into the addressed flag bit, while the “reset flag” instruction loads a zero; and “toggle” changes a zero flag to one or a one flag to a zero. The “flag test” instruction causes the condition latch (COND) to be set only if the tested flag has been previously set, e.g., contains a binary one. Thus the flag bits can be advantageously used to determine whether or not a conditional branch instruction will cause a branch to occur.

Register A and Register B are outputted to display decoder 46 in response to a display instruction command. The contents of Register A contains the digits to be displayed by the display 11 (FIG. 2) and Register B is loaded with bits which indicate the position of the decimal point and whether or not a particular digit is to be blanked. By using Register B to store digit blanking and non-blanking codes along with a decimal point and negative sign codes, which codes are loaded into Register B in accordance with instruction words contained in ROM 30, is another important feature of this invention eliminating the need for using discrete leading zero blanking circuitry, as used in the prior art. The display decoder 46 is connected to output register 47 which provides the digit scan lines to the display 11 via lines 15. The scan generator 36, display decoder 46 and output register 47 cooperate to drive the display 11 (FIG. 2) using the segment scan display technique disclosed by U.S. Pat. application Ser. No. 565,489 filed Apr. 7, 1975, now U.S. Pat. No. 4,014,012, and assigned to the assignee of this invention.

Referring now to FIGS. 4a and 4b, there is shown, in representative form, the timing signals generated by the clock generators 45 implemented on chip 10. The clock generators 45 may be of conventional design, and are not shown in detail herein. The clock generators sequentially generate φ1, P1, φ2 and P2 clock pulses, each pulse having a pulse width time of approximately 0.625 microsecond in this embodiment. The precise frequency of the clock generator is typically “fine tuned” using an external resistor 13 (FIG. 2). A full sequence of the four above-identified clock pulses comprise one state time (S0, S1, S2, etc.), each state time having a duration of approximately 2.5 microseconds in this embodiment. One state time represents the time needed for two bits of a data word to be clocked out of a register. Thus, it requires two state times for a four bit hexadecimal or BCD numeral to be inputted into the arithmetic unit 40 from an operational register 28. Since sixteen digits in all comprise one data word (as is shown in FIG. 6), thirty-two state times (S0-S31) are required to output all sixteen digits from a register. Thus, thirty-two state times (S0-S31) represent one instruction cycle, as is depicted in FIG. 4b, and an instruction cycle has a duration of approximately 80 microseconds in this embodiment. The state times are generated by state time generator 48.

As will subsequently be discussed, the clock is responsive to a decoded display instruction for slowing the speed of the clock during display operations. During display operation, the period of a state time is ten microseconds and the period of an instruction cycle is 320 microseconds.

In addition, clock pulses may be provided at every P1 and P2 time which are simply labeled P and other clock pulses are provided at every φ1 and φ2 time, which are simply labeled φ, as is shown in FIG. 4a. Further, clock pulses are provided at selected P or φ times in selected state times (for instance S1.φ2), as is also exemplified in FIG. 4a.

Referring now to FIGS. 5a and 5b, there is shown diagrammatically in FIG. 5a the ten decimal digits, 0-9, displayable by a seven segment character display along with an eighth segment used as a decimal point. With respect to FIG. 5b, the seven character segments are labeled segments A-G and the decimal point segment is labeled P. For each character position there is a common cathode 9 provided for the eight segments, as is shown in FIG. 5b. The eight segments A-G and P for each character position are respectively connected in common by segment conductors SA -SG and SP. Chip 10 uses segment scanning according to the method disclosed by U.S. Pat. No. 4,014,012, which issued Mar. 22, 1977 wherein the segments are scanned sequentially and the digit cathodes are selectively energized in conjunction with the scanning of the segment electrodes to form the characters 0-9 and a decimal point. By using the segment scanning method of U.S. Pat. No. 4,014,012, the segment amplifiers generally used heretofore in the prior art are eliminated. Thus, chip 10 may be directly interconnected with display 11.

Referring again to FIG. 3, scan generator counter 36 sequentially energizes the SA-SG and SP conductors (FIG. 5b) via lines 14 and pins SEG A-SEG G and SEG P (FIG. 11). Output register 47 is loaded each time a different segment is scanned with a twelve bit binary code indicating whether the cathodes 9 (FIG. 5b), associated with each of the twelve character positions, should be energized via lines 15 and pins D1-D12 (FIG. 11) permitting the scanned segment in the corresponding character positions to actuate.

Referring again to FIG. 6a, there is shown the format of the data word stored in operational registers 38A and 38B and storage registers 39 (FIG. 3). As aforementioned, each data word comprises sixteen digits of serial data, each digit comprising four serial bits. Thus, an entire data word comprises 64 (e.g., 16 × 4) bits. The three most significant digits of the data word preferably comprise the twelve flag bits and the thirteen remaining digits comprise numerical data, the first eleven digits thereof preferably being the mantissa and the least significant two digits being the exponent.

As aforementioned, associating the twelve flag bits with the thirteen digits of numeric data in one data word storage location is an important feature of this invention which eliminates the need for separate flag registers.

In FIG. 6b there is shown the mask codes which are incorporated in many of the instruction words implemented in ROM 30; the set of instruction words storable in ROM 30 and decodable by instruction word decoder logic 31 (FIG. 3) are described in TABLE I. The set of instruction words stored in ROM 30 in this embodiment are listed in TABLE IV. As can be seen from TABLE I, a mask field code (MF) is used in many of the possible instruction words. The mask field denotes to the register selector gates 43 (FIG. 3) which digits of the sixteen digit data words are to be passed to the arithmetic unit 40 (FIG. 3) and which digits are to be recirculated. The mask codes are needed, because it is often desirable to perform some arithmetic or flag logic operation on only the mantissa or only the exponent or both the mantissa and the exponent or on a particular flag bit or perhaps the whole data word. As can be seen from FIG. 6b, there are twelve masks, having codes 0000 through 1011, which are listed and are associated with a rectangle beneath a representation of a sixteen-digit data word. The digits enclosed by the rectangle associated with a particular mask are permitted (by the mask decoder logic 200 (FIG. 8) in instruction word decoder logic 31 when the associated mask code is received) to pass through arithmetic unit 40 while those digits outside the rectangle are recirculated via gates 316a-d (FIG. 9). As will be seen with respect to the detailed discussion of the mask logic (FIG. 8), the mask codes cause the register selector gates 43 (FIGS. 3 and 9) to operate in timed relation with the data being outputted from an operational register 38 in accordance with the state times indicated by state time generator 48 (FIG. 3). The masks of FIG. 6b operate on complete digits, but certain individual bits may be selected by further mask arrangements as will be explained henceforth.

Referring now to FIG. 12, TABLE I, there are shown the set of possible instruction words stored in ROM 30, decoded by instruction word decoder logic 31 and utilized by the remainder of the system. TABLE I refers to FIG. 12 for drawings representative of the various types of instructions. As can be seen, the instruction word comprises thirteen binary bits (I12-I0). A thirteen bit instruction word length provides for the possibility of having up to 213 or approximately 8,000 different instruction codes; however, it will soon be evident that not all these possible instructions are used. Looking first to the first two instructions, namely the “branch on condition” and the “branch unconditionally” instructions, it will be seen that there is a 1 in the I12 position. Since all remaining instructions use a 0 in the I12 position, it will be seen that there are approximately 4,000 variations of the first two instructions. The “branch unconditionally” instruction has a zero in the I11 position following the one in the I12 position and an address in the I10-I0 positions. Since the “branch unconditionally” address contains 11 bits and since the program counter 32a contains 11 bits, the “branch unconditionally” instruction can cause the branch anywhere within ROM 30, including branches between ROM A and ROM B. The “branch on condition” instruction” instruction, on the other hand, contains only a ten bit address because the I10 bit is used as a condition bit. If the state of the condition bit (I10) matches the state of the condition latch, the branch will occur; if there is no match, the branch instruction is ignored. There being only ten bits in the address for the “branch on condition” instruction, when the branch is executed only the ten least significant bits are loaded into the eleven bit address register of program counter 32a. The most significant bit in the program counter remains unchanged. Since a zero in the most significant bit (A10) in the program counter addresses only those instruction words in that part of ROM 30 denoted as ROM A, and a one in the most significant bit (A10) in the program counter addresses only those instruction words located in that portion of ROM 30 denoted as ROM B, the “branch on condition” instruction only permits branching within the confines of either ROM A or ROM B. The unconditional branch instruction may be also considered a “CALL” instruction inasmuch as an incremented address (the location following the location of the unconditional branch instruction) is stored in the subroutine stock 33 if the branch is accomplished.

The next listed instruction words in TABLE I, namely “Branch to R5” and “Return” will be discussed subsequently.

Referring to part five of TABLE I, the operations under mask control contain a zero in the I12 position, the mask field code in the I11-I8 positions, and an operational code in the I7-I0 positions. The operational code is divided into two bit J, three bit K, two bit L, and one bit N fields, as shown in TABLE I. For certain special operations the L and N fields are combined into one three bit field (LN field). TABLE I explains in detail the operations performed in response to particular binary codes entered into the aforementioned J, K, L, and N fields.

Remembering that the mask field, i.e., I11-I8 has only 12 possible mask codes (0000-0101, 0111-1000**, and 1101 and 1111), while a four bit binary number has sixteen possible codes associated therewith, then there are four codes which may be loaded into the mask field position, namely 0110, 1011, 1100 and 1110, which will not be decoded as a mask operation. Two of these four codes, 1110 and 1100, are decoded by instruction word decoder logic 31. The 1110 code is referred to as the miscellaneous non-mask code; the family of instruction words using the miscellaneous non-mask code are explained in Part 6 of TABLE I. The miscellaneous non-mask operations have a four bit Q and four bit P fields in addition to the zero and the I12 position and the 1110 in the I11-I8 positions. In this instruction set, the Q field is ignored by decoder logic 31 unless specifically referred to in this instruction set; the P field is decoded to perform the operations indicated, which are generally operations not making use of the arithmetic unit 40. Thus, these operations relate to transforming data between the storage registers and the operational registers, storing three bit codes in RAB 44 (FIG. 3), storing the contents of R5 register 34 (FIG. 3) in the program counter 32a, or enabling or disabling the BCD corrector in arithmetic unit 40.

The “Return” instruction (Section 4 of TABLE I) and “Branch to R5” location (Section 3 of TABLE I) may be considered as part of the miscellaneous non-mask code since these two instructions also have a 1110 in their I11-I8 positions. The Return instruction causes a branch to the address most recently stored in subroutine stack 33.

Other non-mask operations include the flag operations which are defined by a 1100 in the mask field MF. The flag operations are explained in detail in Part 7 of TABLE I. Although generally referred to as a non-mask operation, the flag operations may be thought of as very detailed mask operation in the calculator disclosed, because a specific flag bit in a data word is examined or operated upon rather than merely operated on a particular one or set of digits using the normal mask codes defined in FIG. 6. Flag operations have not heretofore been thought of as being similar to mask operations, since the flags have been typically stored in special registers of latches separate from the numeric data.

DETAILED DESCRIPTION OF SYSTEM LOGIC DIAGRAM

The various parts of the system of FIG. 3 will now be described with reference to FIGS. 7, 8, 9, 10, 11 and 13 which depict in detail the logic circuit implemented on chip 10 to form the circuits depicted by the block diagrams of FIG. 3. The following discussion with reference to FIGS. 7-11 will refer to the logic signals available at many points on chip 10. It should be remembered that a logical zero corresponds to a negative voltage, that is, Vdd, while a logical one refers to a zero voltage, that is, Vss. It should further be remembered that the P-channel MOS transistors depicted in FIGS. 7-11 become conductive when a logical 0, i.e., a negative voltage, is applied at their respective gates. When a logic signal is referred to which is unbarred, i.e., has no bar across the top of it, the logic signal is to be interpreted as “true” logic; that is, a binary one indicates the presence of the signal (Vss) whereas the binary zero indicates a lack of the signal (Vdd). Logic signal names including a bar across the top thereof are in “false” logic; that is, a binary 0 (Vdd voltage) indicates the presence of the signal whereas a binary 1 (Vss voltage) indicates that the signal is not present. FIGS. 7-11 do not depict the clock generators implemented on chip 10, the clocks generating clock pulses φ1, P1, φ2, P2, in accordance with the clocking signals depicted in FIG. 4a. The clock generators are of conventional design and are responsive to decoded display instruction command signal for decreasing the frequency of the clock, as aforementioned.

THE ROM AND PROGRAM COUNTER

Referring now to FIG. 7, there is shown the logic diagram of the program counter 32a, the branch logic 32b, subroutine stack 33, condition latch 41, test logic, and ROM 30 along the interconnecting circuitry. The details of ROM 30 are not shown in detail in FIG. 7, however, ROM 30 is of the virtual ground type disclosed in U.S. Pat. No. 3,934,233 by Roger J. Fisher granted Jan. 20, 1976. Using the virtual ground read-only-memory of U.S. Pat. No. 3,934,233 permits the size of the ROM to be significantly reduced in comparison with the ROM’s typically used in the prior art by using one ground or Vss line for five or more P defusions. Lines A0-A10 supply, in parallel, at time S22.φ1, the eleven bit address for addressing ROM 30. Address lines A0 -A6 address the X address decoder disclosed in U.S. Pat. No. 3,934,233 while address lines A7 -A10 address the Y address decoder of U.S. Pat. No. 3,934,233. Lines I12 -I0 provide, in parallel, the instruction word corresponding to the address appearing on address lines A0 -A10. The false logic instruction word is clocked out of ROM 30 at S29.φ2 by gates 111 and inverted to true logic by inverters 110. Address lines A10 -A0 are loaded from program counter 32a at S22.φ1 by gates 112, unless the power up clear latch 162 has inserted a logical one into complex gate 113, which in turn inhibits conduction by gates 112. The power up clear latch 162 is preferably incorporated in clock 45 and comprises a latch which preferentically enters a first state for generating the logical one to complex gate 113 when power is initially applied to the system. The state of the latch changes when the clocks turn on sufficiently to change a capacitor associated with the reset input to the latch.

Gates 114 unconditionally precharge address lines A0 -A10 to Vdd at S21.φ2 of each instruction cycle and when power up-clear logic finally inserts a zero into complex gate 113, the address previously received by ROM 30 is 000000000002. Thus, power up-clear logic effectively forces the ROM to branch to the very first location contained therein. This automatic branch to 00016 using the ROM precharge gates 114 in combination with gates 113 is an important feature of this invention which permits the operational registers 38 and storage register 39 along with the remaining logic circuitry to be prepared for numeric operations in accordance with instruction words loaded into ROM 30 beginning at location 00016 rather than using dedicated circuitry therefore or requiring an address to be jammed into program counter 32a after the state of the PUC signal changes.

Program counter 32a comprises an eleven bit shift register, having twenty-two inverter stages 115 and gates 116 for precharging the stages, for forming an address register. A serial input to program counter 32a is received on line 117 and a serial output is communicated via line 118 to add-one circuit 119. Gates 143 interconnect the eleven stages of program counter 32a in series. Add-one circuit 119 is a simplified serial add-one circuit comprising a NAND gate 119a, one input of which is connected to line 118 and an output of which is connected to inverter 119b. The output from inverter 119b is communicated to another input of NAND gate 119a, to the gate electrode of transistor 119c and the source electrode of transistor 119d. Line 118 is further connected to the source electrode of transistor 119c and the gate electrode of transistor 119d. The drain electrodes of transistors 119c and 119d are connected together and normally provide the previous eleven bit program counter address incremented by the number one on line 120. The junction between the output of NAND gate 119a and the input of inverter 119b is further interconnected with the HOLD signal generated by gate 500 (FIG. 11) and gate 291 (FIG. 8) to inhibit incrementing the previous program counter address by add-one circuit 119.

The output from add-one circuit 119 normally recirculates via line 120 and gate 121 back to the input of program counter 32a on line 117. Gate 121 is responsive to the output from NAND gate 130 and is normally conductive except when inhibited by a RETURN or KB BRANCH (Branch to R5) commands. Program counter 32a may also be loaded with either ten or eleven bits of the instruction word appearing at gates 110 via lines 122 and gates 123 and 124. When a conditional branch instruction word is decoded and branch logic 32b determines that the condition has been satisfied, the new branch address is loaded from the I0-I9 bits of the instruction word into the A0-A9 bits of program counter 32a via lines 122 and gates 123. When an unconditional branch instruction word (CALL) is decoded, gate 124 is caused to conduct at the same time as gates 123, thereby inserting eleven bits from the instruction word (I0-I10) into program counter 32a. The ten or eleven bits from the instruction word are loaded into program counter 32a after the prior ROM address plus one has recirculated serially via lines 117, 120 and gate 121.

THE SUBROUTINE STACK

The subroutine stack 33 is a three-level stack of eleven bit shift registers 33a, 33b, and 33c, each comprised of twenty-two inverter stages 125. Except when subroutine stack 33 is either outputting a return address to program counter 32a or receiving an address from program counter 32a, the eleven bit addresses stored therein are recirculated via gates 126. Gates 126 normally receive a logical zero (i.e., are made conductive) from NAND gate 137, which provides a logical one output only upon receiving either a RETURN signal from NAND gate 135 or a CALL signal from NAND gate 136.

When an unconditional branch instruction is decoded by branch logic 32b, the CALL signal goes to zero permitting the present ROM address plus one to be loaded into subroutine stack register 33a via line 120 and gate 127 from add-one circuit 119. Addresses previously loaded into subroutine stack/registers 33a and 33b are shifted to registers 33b and 33c, respectively, by gates 128. Gates 127 and 128 are responsive to the CALL signal. If an address had previously been loaded into subroutine stack register 33c, it would have been lost upon the execution of another unconditional branch instruction.

Upon the decoding of a “Return” (RTN) instruction by decoder 214 (FIG. 8), the RETURN signal from NAND gate 135 goes to logical zero, thereby causing the output of NAND gate 130 to become a logical one, interrupting the normal insertion of an up-dated address via line 120 when gate 121 becomes nonconductive and forcing the contents of subroutine stack register 33a to be inserted into program counter 32a via gate 129 and line 117. Gates 131 cause the contents of subroutine stack register 33b to be inserted into register 33a and the contents of register 33c to be inserted into register 33b upon the execution of a return instruction. Gates 131 are responsive to the RETURN signal from NAND gate 135.

THE BRANCH LOGIC AND CONDITION LATCH

Branch logic 32B and condition latch 41 cooperate to control gates 123 and 124 in program counter 32a for inserting the address portion of a branch instruction word into program counter 32a. NAND gates 132 from the latch circuit of the condition latch 41 and are responsive to an ADDER COND SET signal from gate 401 (FIG. 10) and a LOAD R5 signal from decoder 508c (FIG. 11) for letting the latch. The latch is reset by either a Return or by such instruction, as is explained subsequently. Complex gates 133 are responsive to COND and COND signals produced by NAND gates 132, a PREG signal from NAND gate 146 and the I10, I10, I11 and I12 bits which are derived from ROM 30, the I10 bit via inverter 134. OR gates 133a and 133b both provide a logical one output only when the state of the condition bit matches the state of the I10 bit. Thus, the output from OR gates 133a and 133b along the I12 and I11 bits and the PREG signals are supplied to AND gate 133c which provides a logical one output only when (1) I11 and I12 indicates that a conditional branch instruction has been outputted from ROM 30, (2) the state of the I10 bit and COND match and (3) PREG is a logical one indicating that the PREG test circuitry is not activated. The test circuitry and the PREG and TIRG signals associated therewith are described subsequently.

NAND gate 136 is responsive to the I12 and the I11 bits and to PREG thereby providing a CALL signal to NAND gates 137 and 138 and to gates 127 and 128 unless the test circuitry has been activated. NAND gate 135 is responsive to the RTN signal from decoder 214a (FIG. 8) via inverter 159 and to the PREG signal for generating the RETURN signal which is a logical zero if (1) a “return” instruction has been decoded and (2) the PREG test circuitry has not been activated.

NAND gate 138 is responsive to CALL from NAND gate 136 and to TIRG for generating a CALL signal which is normally a logical zero unless (1) an unconditional branch (call) instruction has been decoded or (2) the test circuitry has been activated. NAND gate 139a, which normally receives an S20.P1 clock signal via gate 149 in addition to the CALL signal from NAND gate 138, provides a CALL signal at S20.P1 to complex gates 139b. NAND gate 139a is responsive to an S30.P1 clock signal in gate 150 in lieu of the S20.P1 signal if the test circuitry is activated. Complex gates 139b output the CALL signal at S21.φ1 to gate 124, unless the test circuitry is activated, in which case the CALL signal is supplied to gate 124 at S31.φ1. OR gate 133d is responsive to the output from AND gate 133c and to CALL from NAND gate 138, thereby producing a logical one output upon the occurrence of either: (1) a condition/I10 match on a conditional branch instruction, or (2) the CALL signal (on an unconditional branch instruction or PREG test mode operation). The output of OR gate 133d is supplied to NAND gate 133e along with a normal S20.P1 signal from gate 149 (or S30.P1 during TIRG test operation). NAND gate 133e, in conjunction with gates 140, provide a BRANCH signal at S21.φ1 (S30.P1 in test mode) to gates 123 for inserting the I0-I9 bits of the instruction word into program counter 32a.

Inverter 142 outputs a RETURN signal from the RTN signal received from decoder 214a (FIG. 8). Gates 141 are responsive to the I12 branch bit, the RETURN signal from inverter 142 and the S20.φ1 signal fro resetting the condition latch 141 upon the occurrence of either (1) a branch instruction (e.g., I12 = 1) or (2) upon a “return” instruction.

Considering now the timing of the addressing operations of program counter 32a during normal operations, the address stored in program counter 32a is incremented in add-one circuit 119. The incremented address is circulated back into the program counter 32a during S2-S12.φ1 when gates 143 in program counter 32a are clocked. Thus, the incremental address in program counter 32a is updated by state time S12 of an instruction cycle and will normally be clocked into ROM 30 at the following S22.φ1 by gates 112 for reading out the next instruction word. If a conditional BRANCH (and the condition is satisfied) operation is indicated by the present instruction word read from ROM 30 (at the previous S29.φ2), the present address in program counter 32a is still incremented by add-one circuit 119 during S2-S12, but the address portion of the BRANCH instruction word is jammed into program counter 32a by the action gates 123 and 124 at S21.φ1, thereby inserting a new address one state time before the new address is to be clocked at S22.φ1 into ROM 30. This one state time is sufficient to precharge and conditionally discharge the inverters 115 making up the stages of program counter 32a. During a CALL operation, the incremented address is stored in the subroutine register 33a, and a new address from the I0 -I10 bit of the CALL instruction word is clocked into program register 32a, a manner similar to the inputting of a BRANCH address.

THE TEST CIRCUITRY

NAND gate 146 is responsive to TEST and K1 signals which are clocked on S31.φ1 to provide at its output PREG. NAND gate 147 is likewise responsive to TEST and K1 but is clocked at S0.φ1 to provide TRIG which is inverted to TRIG by inverter 148. PREG is generated when a ROM address is desired to be inputted directly to program counter 32a via keyboard line K1 for test purposes. TIRG is also generated if the instruction word at the aforementioned address is desired to be serially readout of the chip on line K2 during test operations. The output from inverter 148 is supplied to gate 149 which supplies the S20.P1 clock signal to NAND gates 133e and 139a, the S20.P1 clock signal being the clock signal used during non-TIRG test operations. The TIRG signal, besides being applied as an input to NAND gate 138 is also supplied to gate 150 for supplying the S30.P1 clock signal to NAND gates 139a and 133e, the S30.P1 clock signal being provided during TIRG test operations. PREG is inverted by inverter 151 whose output is connected to gate 145, which is in line 117. Gate 145 is conductive, except during test mode operations, normally permitting the incremented address to recirculate on line 117. Thus, gate 145 inhibits the incremented address outputted from add-one circuit 119 from being inserted into program counter 32a during test mode operations. Instead, the address to be inserted on line 117 during test mode operations is received from keyboard line K1 (FIG. 11) via gate 152 which is responsive to PREG. The output from program counter 32a is supplied to keyboard line K2 (FIG. 11) via line 118, inverter 153 and gates 601 and 602 (FIG. 13). K2 receives, as it will be subsequently shown, the I0 -I10 bits of the instruction word addressed in ROM 30 during state times S2- S12 of TRIG test mode operations. Accordingly, the output from program counter 32a on line 118 is clocked at S2-S12 to inverter 153 via gate 154. The I11 and I12 bits of the instruction word are also outputted to K2, these bits being outputted during S13 and S14 via gates 155 and 156, respectively, which provide the I11 and I12 bits to the input of inverter 153.

As will be shown, the aforementioned PREG and TIRG test circuitry permits the instruction words implemented ROM 30 to be read out of the chip on line K2 according to addresses inserted into the chip via line K1 when the calculator has been put into a test mode via input signals which are discussed with reference to FIG. 13. Once in the PREG test mode, an address may be inserted into program counter 32a from K1 via gate 152. This insertion would be timed to be inserted into program counter 32a in the same manner as an updated address from add-one circuit 119. Any branching which might occur at the same time a PREG test operation address is inserted into program counter 32a (according to the previously addressed instruction word) is inhibited by the PREG inputs to AND gate 133c and NAND gate 136. Thus, as the old address is shifting out of the program counter 32a on line 118, an externally supplied address is being inputted from K1 via gate and 152 and line 117 during the same instruction cycle. The incremented address is blocked by the action gate 145. This externally supplied address is then used to address ROM 30 at the following S22.φ1.

If the chip is also placed into the TRIG test mode (in addition to PREG), the I0 -I10 bits of the instruction word are clocked intp program counter 32a via gates 124 and 123 at S31.φ1, it being remembered that the CALL S21φ1 and BRANCH S21.φ1 signals are automatically activated at S31φ1 during TIRG test mode operations. The I0-I10 bits instruction word are then shifted out of program counter 32a at (S2-S12), φ1 via line 118, gate 154 and inverter 153. At the same time a new address is inputted from K1 via gate 152. Thus, during each instruction cycle, an external source may be used to address ROM 30 and the code contained in ROM 30 at that address is read out via K2, the I0 -I10 bits being provided by program counter 32a and the I11 and I12 bits being provided by gates 155 and 156. It should be evident that the entire contents of the ROM 30 may be checked in approximately 2,000 instruction cycles whereas if the contents of ROM 30 were to be checked by requiring the calculator to perform all possible instructions, it should be evident that that technique would require significantly more than 2,000 instruction cycles.

Additionally, the state of the condition latch 41 is outputted as COND to keyboard line K3 (FIG. 11) via an inverter 160, responsive to latch 41, and gates 605-608 (FIG. 13). Similarly, HOLD is outputted to keyboard line K3 during test mode operations via gates 605, 607 and 608 (FIG. 13).

Referring now to FIG. 13, there is shown the test logic associated with keyboard lines K1-K4. The K1-K4 pins depicted in FIG. 13 are the same pins as the K1-K4 pins depicted in FIG. 11. The address received on line K1 is directly connected to the input to gate 152 (FIG. 7). The instruction word received from the ROM is outputted via gates 601 and 602 to pad K2. Gates 603 and 604, which are responsive to TEST AND TEST, respectively, isolate the instruction word output from line K2 except during test operations.

Pin K4 is responsive to a Vdd signal for producing the TEST signal. Pin K4 supplies one input to NOR gate 609. The other input to NOR gate 609 is derived from S28.φ1. The output from NOR gate 609 is supplied through an inverter 610 and gate 611 to NAND gate 612. The other input of NAND 612 is responsive to the power up clear signal, PUC. The output of NAND gate 612 provides the TEST signal and via inverter 613 the TEST signal.

Pin K3 is responsive to the HOLD and COND signals produced by the calculator when in a test mode. Accordingly the HOLD and COND signals are provided via gates 605 and 606, respectively, clocked at state times S3 and S2, respectively, to a gate 604 which is responsive to TEST. The output from gate 607 drives a gate 608 for providing a signal to pin K3 during test operations indicative of HOLD and COND.

THE INSTRUCTION WORD DECODER LOGIC

The instruction word decoder logic 31 is shown in FIG. 8. Referring now to FIG. 8, a decoder 200, which decodes the mask portion of instruction field, receives from inverters 110 (FIG. 7) the mask field (MF) of the instruction word, i.e., bits I11 -I8, and their complements I11 -I8. Decoder 200 is also responsive to the B-E (and complements B-E) outputs from state time generator 68 (FIG. 11), which provides a binary representation of which one of the 32 state times this system is operating in. Since there are sixteen digits in a data word and since the first digit, (D0) starts imputting at S0, then the second digit begins inputting at S2 and so on. Decoder 200 decodes the aforementioned bits to produce the masks MANT, LLSD, etc (FIG. 6b). In addition, decoder 200 decodes the I12 bit, thereby disabling decoder 200 when I12 is a logical zero (I12 is a logical one then), when a conditional or unconditional branch instruction has been outputted from ROM 30 (FIG. 7). Decoder 200 decodes the twelve mask codes which are explained with reference to FIG. 6. Remembering that a mask code indicates which bits of a data word are to be operated on by arithmetic unit 40 and which are to be merely recirculated by register selector gates 43, it is desirable that when a particular mask field has been decoded by decoder 200 that a mask signal be generated during the state times at which the particular digit of a word is to be operated on by arithmetic unit 40 in accordance with the mask codes defined in FIG. 6. Therefore, decoder 200 is responsive not only to the MF field (bits I11 -I8 of the instruction word), but also to the binary representation of which one of the 32 state times the system is operating in. Since the digits are outputted only at even state times, as aforementioned, decoder 200 need not be responsive to the least significant bit from state time generator 48 on line A or A.

Decoder 201, which is associated with decoder 200, is responsive to the I11 -I8 bits of the instruction word and their complements, I11 -I8 and in addition the I12 bit to disable the decoder 201 when a conditional or unconditional branch instruction has been outputted from ROM 30 (FIG. 7). Decoder 201 decodes the miscellaneous (MISC) and flag operation (FLGOP) codes which also occupy the MF field, as is explained with reference to TABLE I, Sections 6 and 7. As will be seen, the outputs from decoder 201, MISC (via inverter 203) and FLGOP (as well as FLGOP via inverter 211), are applied as inputs into several other decoders for disabling or enabling signals during miscellaneous or flag operations.

Decoder 210 receives bits I0 -I3 and their complements I0 -I3 of the instruction word and it is enabled only during miscellaneous operations by MISC which is derived from decoder 201 via inverter 203. Decoder 210 decodes the stack instructions (STAY, STAX, STYA, AND STXA) and the address buffer instruction (NAB and RAB), which are explained in TABLE I, Section 6.

Decoders 204 and 205 decode the bit and digit defining bits, respectively, for the flag instructions (see TABLE I, Section 7, B and D fields). Decoder 204 is responsive to the A and A state time from state time generator 48 (FIG. 11), φ1 and φ2 clock pulses (which are applied to separate loads 204a and 204b associated with decoder 204) and the flag bit defining bits I2 -I3 of the B field of the flag instruction (see TABLE I, Section 7). The I2 -I3 bits define which bit of four in a digit is selected and decoder 204 provides enabling signal when there is a match between (1) the bit selected and (2) the time at which that bit enters arithmetic unit 40 as denied by the P1 and P2 clocks and by whether the state time is odd or even as defined by state time A. Decoder 205 decodes the digit selected (as defined by bits I4 -I5 of the flag instruction, see TABLE I, Section 7) and is responsive to the B-E and B-E outputs from state time generator 48 (FIG. 11) for generating an enabling signal when there is a match between (1) the digit selected and (2) the time at which that digit enters arithmetic unit 40. The output from decoder 204 is nanded in decoder 216 onto line 213 and the output from decoder 205 is nanded in decoder 216 onto line 217. Lines 213 and 217 are applied to NAND gate 207 whose output is connected to input of NOR gate 212. The other input of NOR gate 212 is FLGOP from decoder 201 and thus NOR gate 212 provides a logical one output upon the decoding of flag operation instruction during the time that the bit selected in decoder 204 within the digit selected in decoder 205 is outputted from the operational registers 38 into arithmetic unit 40. The output from the mask field decoder 200 is applied to decoder 202 for performing a NAND operation thereby providing an output on line 218 of a logical zero except when (1) a mask operation has been decoded and (2) the state time counter 48 indicates that the selected bits are to be inputted to arithmetic unit 40. The outputs of NOR gates 212 and 218 are applied to the inputs of NOR gate 219 which outputs a logical one except during either (1) arithmetic mask operations decoded by decoder 200, or (2) flag bit mask operations decoded by decoders 204 and 205. It should be appreciated that the arithmetic masks and flag masks are generated slightly ahead of the time the selected digit or bit is outputted from an operational register to provide sufficient time for the MOS gates to be actuated. The output from NOR gate 219 is outputted through a series of gates 220 providing a signal MSK φ which is outputted to the arithmetic unit one φ time before the corresponding data is inputted to the adder. The output from NOR gate 219 is also inverted by an inverter 222 to provide a MASK φ signal to mask delay generator 225, NAND gate 230, and gate 223, inverter 250 and gate 251.

A mask delay generator 225, whose function is more fully described with respect to the operational register selector gates 43, comprises a series of clocked inverters for providing a delayed mask signal in both true and false logic, the MD φ/P signal being two state times behind the MASK φ signal provided by inverter 222. The MDφ signal is one φ time earlier than the normal MD φ/P signal and an MDP signal is provided which provides a P clock during the occurrence of an MDφ/P signal.

Decoder 215 is responsive to the FLGOP signal and the I0 -I5 bits (and their complements) of the instruction word for decoding the STORE signal (see TABLE I, Section 3, the LN field), the SHIFT signal, the IR5 signal and the 2R5 signal (see TABLE I, Section 5, K field). Decoder 206 is responsive to the MISC signal and the I0 -I2 bits instruction word for generating the BCDS and BCDR signals, which are indicative of whether the arithmetic unit is the BCD correct (see TABLE I, Section 6). These signals are applied to separate NAND gates 228 and 229 which are arranged as a latch. The output from this latch is the HEX signal which is indicative of whether the adder is to add in hexidecimal or is to BCD correct.

Decoder 208 is generally responsive to selected I0 -I4 bits of the instruction word and provides a T/T output and a K→Y output. The T/T signal is generated during flag operations when a flag is to be tested or toggled while the K→Y signal is generated during non flag operations when the number one is desired to be loaded into the least significant masked digit position in the Y input of arithmetic unit 40. The K→Y signal is inverted by inverter 252 and applied to one input of AND gate 251. AND gate 251 is also responsive to the MASK φ signal from inverter 222 and to a delayed MASK φ signal supplied by inverter 250. Thus, upon occurrence of a K→Y signal and a MASK φ signal, AND gate 251 is effective for inserting a one into the least significant bit of the least significant digit immediately following the beginning of the MASK φ signal. The T/T signal, as will subsequently be seen, is also used to insert a one into the appropriate bit position in the Y input to arithmetic unit 40; thus the T/T is inverted by inverter 224 and applied as an input to NOR gate 226. The other input to NOR gate 226 is from the output of AND gate 251. NOR gate 226 drives a series of gates 231 which are effective for inserting the aforementioned one into the appropriate bit position in the Y input to the arithmetic unit 40.

Decoder 209 decodes the BRK signal which causes a branch to occur in branch logic 32b, the branch location being defined by the contents of R5 register 34 (FIG. 10). Referring again to FIG. 7, the BKR signal is supplied as an input to NAND gate 130 interrupting the normal address recirculation path via lines 120 and 117 for the updated address. BKR also closes gate 157 for inserting the contents of R5 register 34 via inverter 158 onto line 117 for insertion into program counter 32a via gate 145. Returning to FIG. 8, NAND gate 209a generates the S/RS signal which is generated during flag operations for setting or resetting a flag and the DISP signal which is generated during display operations.

Decoder 214 is responsive to the I7 -I0 bits of the instruction word and to FLGOP, FLGOP, and MISC signals for generating the signals used to operate the various register selector gates and register recirculation gates. Decoder section 214a generates the RTN (return) signal which is supplied to inverter 142 and to NAND gate 135 (FIG. 7). Decoder section 214b generates AX-DX signals and section 214c generates AY-DY signals, which are inverted by inverters 221. AX-DX and AY-DY signals are supplied to NAND gates 231a-231d and 232a-232d, respectively, and are indicative of which ones of the operational registers A-D are to be interconnected with the X and Y inputs to the arithmetic unity using the register selector gates 43 (FIG. 9). NAND gates 231a-231d are also responsive to the GMASK signal on line 234 and to the STORE signal generated by decoder 215. NAND gates 232a-232d are also responsive to GMASK signal on line 296. The purpose of the STORE and GMASK signals, in respect to these aforementioned NAND gates, and the timing interactions of these gates with respect to movement data within the various operational registers, between the operational registers and with arithmetic unit via register selector gates 43 will be explained subsequently with reference to FIG. 9. The 214d portion of decoder 214 decodes the I0-I2 bits of the instruction word, those bits corresponding to the L and LN fields in the instruction words control the operations under mask control (Table I, Section 5) for generating the EXCH, Σ→K and Σ→J signals. The Σ→J signal is indicative of a decoded instruction indicating that the results from the arithmetic unit 40 on line Σ’ is to go to the register defined by the J field and similarly the Σ→K signal indicates that the results from the arithmetic unit 40 on line Σ’ is to go the register defined by the K field, or neither field, in which case a binary 10 occurs in the L field, which is simply not decoded by decoder 214 (See Table I, Section 5). Decoder 214e is responsive to the FLGOP and I1 and I0 bits of the instruction word for decoding the TGL (TOGGEL) signal which is used invert a selected flag bit.

The EXCH, Σ→K, Σ→J, TGL, STORE, and S/RS signals are supplied to a decoder 227 whose outputs are supplied to decoder 238 along with the AX-DX and AY-DY signals from inverters 221 and the SR’ signal from NOR gate 237. The outputs from decoder 238 are applied as inputs to decoder 239 for decoding the recirculation signals RA, RB, RC, and RD and the adder output signals ΣA, ΣB, ΣC, and ΣD. The RB-RD recirculation signals are inverted to true logic by inverters 236. The RB-RD signals are supplied to NOR gates 235b-235d, respectively, along with a RECMASK signal from NAND gate 247 for producing RECB-RECD signals. The recirculation signal RA is supplied to an input of OR gate 244 along with the EXCH’ signal derived from decoder 214 via NAND gate 240, which is also responsive to S1. The output of OR gate 244 supplied to a NAND gate 247 via an inverter 248. The output of NAND gate 245 is supplied to NAND gate 246 for producing a RECA signal. NAND gate 246 is also responsive to the LA (Load A) signal from inverter 249 indicating that the contents of one of the storage registers is to be outputted to operational register A.

The ΣA-ΣD outputs from decoder 239 are supplied to NAND gates 233a-233d, respectively, for generating Σ→A-Σ→D signals which are used to control selector gates 43 for determining to which one of the operational registers A-D the result outputted on line Σ’ from arithmetic unit 40 is to be communicated. NAND gates 233a-233d are also responsive to the MD signal from the output of the mask delay generator on line 253.